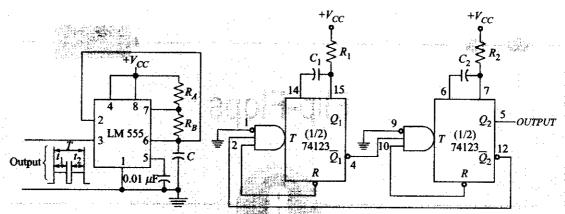

Work element: Study the working of IC 555 and 74123, and understand the different input outputs. From above relations, calculate the resistance and capacitance values. See the waveform in oscilloscope. Calculate duty cycle from the oscilloscope reading and compare with theoretical value. Conduct similar exercise for 74123 based circuit as shown. Repeat the experiment with other combinations of resistance and capacitance values.

# Answers to Self-tests

a sagadiga

- 1. An input is sensitive to PTs, and the circuit (no phase shift). Inverting: 180° phase shift output changes synchronously with PTs. The circuit output changes in synchronism

- 2. It means that a circuit input is sensitive to PTs. (See Fig. 7.6b.) The thirties that a trial pack fan.

- NTs is a bubble in front of a dynamic input indicator. (See Fig. 7.7b.)

- 4. A series mode offers low impedance at resonance, thus providing positive feedback for oscillation. A parallel mode offers high impedance at resonance, and thus provides insufficient feedback to produce oscillation. The the improved the angle of the 15. Nonretriggerable while the interest of the control o

- 5. Unnecessary. They simply simulate a load the first 16. True that the same that the condition with a regarded and a price in the action of the total of the condition with the condition of the

- 6. It means that the circuit has two input 18. Glitches are the unwanted pulses appearing contrast, a simple inverter has only a single 19. A strobe pulse is a pulse timed to eliminate threshold voltage level.

- 7. Noninverting: the input and output are both high (or both low) at the same time

- between input and output.

- 8. Schmitt triggers can be used to clean up a noisy signal or to change a signal having a slow rise time into one having a fast rise Filings many ing MagNaka and A Napib time.

- 3. The logic symbol for an input sensitive to 9. A circuit has two output states, neither of which is stable.

- Dec **10**0 **11 rue**s de Africanes de Petrolitation de la Carte

- 11. Inversely

- 12. A circuit has two output states, one of which is stable.

- 13. True

- 14. The stable state is low.

- threshold voltage levels—an upper at the output of a gate when two or more threshold and a lower threshold. By inputs change state simultaneously.

- 化多类的 医第三次静脉 经放弃 电电流分离

# Flip-Flops

- ◆ Describe the operation of the basic RS flip-flop and explain the purpose of the additional input on the gated (clocked) RS flip-flop

- ◆ Show the truth table for the edge-triggered. RS flip-flop, edge-triggered D flip-flop, and edge-triggered JK flip-flop

- ♦ Discuss some of the timing problems related to flip-flops

- ◆ Draw a diagram of a JK master-slave flip-flop and describe its operation

- ◆ State the cause of contact bounce and describe a solution for this problem

- ◆ Describe characteristic equations of Flip-Flops and analysis techniques of sequential circuit

- ◆ Describe excitation table of Flip-Flops and explain conversion of Flip-Flops as synthesis example

The outputs of the digital circuits considered previously are dependent entirely on their inputs. That is, if an input changes state, output may also change state. However, there are requirements for a digital device or circuit whose output will remain unchanged, once set, even if there is a change in input level(s). Such a device could be used to store a binary number. A flip-flop is one such circuit, and the characteristics of the most common types of flip-flops used in digital systems are considered in this chapter. Flip-flops are used in the construction of registers and counters, and in numerous other applications. The elimination of switch contact bounce is a clever application utilizing the unique operating characteristics of flip-flops. In a sequential logic circuit flip-flops serve as key memory elements. Analysis of such circuits are done through truth tables or characteristic equations of flip-flops. The analysis result is normally presented through state

table or state transition diagram and also through timing diagram. Conversion of flip-flop from one kind to another can be posed as a synthesis problem where flip-flop excitation tables are very useful.

### 8.1 RS FLIP-FLOPS

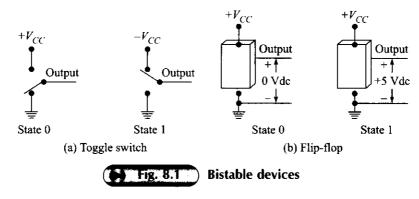

Any device or circuit that has two stable states is said to be *bistable*. For instance, a toggle switch has two stable states. It is either up or down, depending on the position of the switch as shown in Fig. 8.la. The switch is also said to have *memory* since it will remain as set until someone changes its position.

A flip-flop is a bistable electronic circuit that has two stable states—that is, its output is either 0 or +5 Vdc as shown in Fig. 8.1b. The flip-flop also has memory since its output will remain as set until something is done to change it. As such, the flip-flop (or the switch) can be regarded as a memory device. In fact, any bistable device can be used to store one binary digit (bit). For instance, when the flip-flop has its output set at 0 Vdc, it can be regarded as storing a logic 0 and when its output is set at +5 Vdc, as storing a logic 1. The flip-flop is often called a *latch*, since it will hold, or latch, in either stable state.

### **Basic Idea**

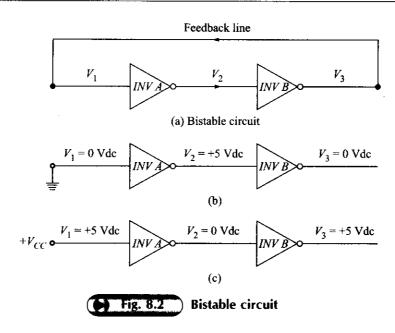

One of the easiest ways to construct a flip-flop is to connect two inverters in series as shown in Fig. 8.2a. The line connecting the output of inverter B (INV B) back to the input of inverter A (INV A) is referred to as the feedback line.

For the moment, remove the feedback line and consider  $V_1$  as the input and  $V_3$  as the output as shown in Fig. 8.2b. There are only two possible signals in a digital system, and in this case we will define L=0=0 Vdc and H=1=+5 Vdc. If  $V_1$  is set to 0 Vdc, then  $V_3$  will also be 0 Vdc. Now, if the feedback line shown in Fig. 8.2b is reconnected, the ground can be removed from  $V_1$ , and  $V_3$ , will remain at 0 Vdc. This is true since once the input of INV A is grounded, the output of INV B will go low and can then be used to hold the input of INV A low by using the feedback line. This is one stable state— $V_3=0$  Vdc.

Conversely, if  $V_1$  is +5 Vdc,  $V_3$  will also be +5 Vdc as seen in Fig. 8.2c. The feedback line can again be used to hold  $V_1$  at +5 Vdc since  $V_3$  is also at +5 Vdc. This is then the second stable state—  $V_3$  = +5 Vdc.

### **NOR-Gate Latch**

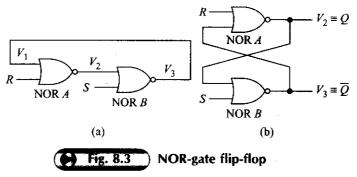

The basic flip-flop shown in Fig. 8.2a can be improved by replacing the inverters with either NAND or NOR gates. The additional inputs on these gates provide a convenient means for application of input signals to

switch the flip-flop from one stable state to the other. Two 2-input NOR gates are connected in Fig. 8.3a to form a flip-flop. Notice that if the two inputs labeled R and S are ignored, this circuit will function exactly as the one shown in Fig. 8.2a.

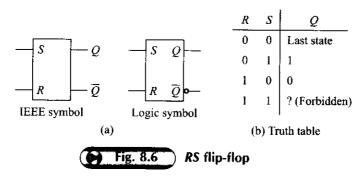

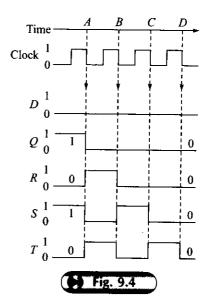

This circuit is redrawn in a more conventional form in Fig. 8.3b. The flip-flop actually has two outputs, defined in more general terms as Q and  $\overline{Q}$ . It should be clear that regardless of the value of Q, its complement is  $\overline{Q}$ . There are two inputs to the flip-flop defined as R and S. The input/output possibilities for this RS flip-flop are summarized in the truth table in Fig. 8.4. To aid in understanding the operation of this circuit, recall that an H=1 at any input of a NOR gate forces its output to an L=0.

- 1. The first input condition in the truth table is R = 0 and S = 0. Since a 0 at the input of a NOR gate has no effect on its output, the flip-flop simply remains in its present state; that is, Q remains unchanged.

- 2. The second input condition R = 0 and S = 1 forces the output of NOR gate B low. Both inputs to NOR gate A are now low, and the NOR-gate output must be high. Thus a 1 at the S input is said to SET the flip-flop, and it switches to the stable state where Q = 1.

- 3. The third input condition is R = 1 and S = 0. This condition forces the output of NOR gate A low, and since both inputs to NOR gate B are now low, the output must be high. Thus a 1 at the R input is said to RESET the flip-flop, and it switches to the stable state where Q = 0 (or  $\overline{Q} = 1$ ).

- 4. The last input condition in the table, R = 1 and S = 1, is forbidden, as it forces the outputs of both NOR gates to the low state. In other words, both Q = 0 and  $\overline{Q} = 0$  at the same time! But this violates the

| R | S | Q          | Action    |

|---|---|------------|-----------|

| 0 | 0 | Last state | No change |

| 0 | 1 | 1          | SET       |

| 1 | 0 | 0          | RESET     |

| 1 | 1 | ?          | Forbidden |

Fig. 8.4

Truth table for a NORgate RS flip-flop

basic definition of a flip-flop that requires Q to be the complement of  $\overline{Q}$ , and so it is generally agreed never to impose this input condition. Incidentally, if this condition is for some reason, imposed and the next input is R = 0, S = 0 then the resulting state Q depends on propagation delays of two NOR gates. If delay of gate A is less, i.e. it acts faster, then Q = 1 else it is 0. Such dependence makes the job of a design engineer difficult, as any replacement of a NOR gate will make Q unpredictable. That's why R = 1, S = 1 is forbidden and truth table entry is ?.

It is also important to remember that TTL gate inputs are quite noise-sensitive and therefore should never be left unconnected (floating). Each input must be connected either to the output of a prior circuit, or if unused, to GND or  $+V_{CC}$ .

Example 8.1

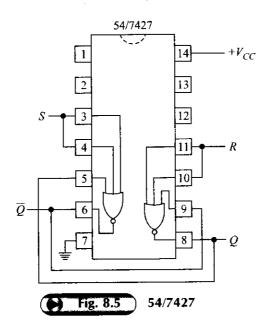

Use the pinout diagram for a 54/7427 triple 3-input NOR gate and show how to connect a simple RS flip-flop.

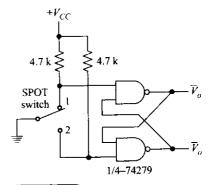

Solution One possible arrangement is shown in Fig. 8.5. Notice that pins 3 and 4 are tied together, as are pins 10 and 11; thus no input leads are left unconnected and the two gates simply function as 2-input gates. The third NOR gate is not used. (It can be a spare or can be used elsewhere.)

The standard logic symbols for an RS flip-flop are shown in Fig. 8.6 along with its truth table. The truth table is necessary since it describes exactly how the flip-flop functions.

### NAND-Gate Latch

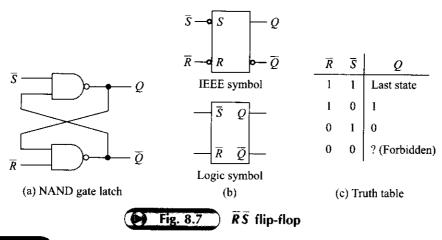

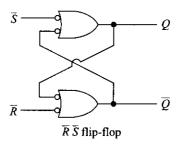

A slightly different latch can be constructed by using NAND gates as shown in Fig. 8.7. The truth table for this NAND-gate latch is different from that for the NOR-gate latch. We will call this latch an  $\overline{RS}$  flip-flop. To understand how this circuit functions, recall that a low on any input to a NAND gate will force its output high. Thus a low on the  $\overline{S}$  input will set the latch  $(Q = 1 \text{ and } \overline{Q} = 0)$ . A low on the  $\overline{R}$  input will reset it (Q = 0). If both  $\overline{R}$  and  $\overline{S}$  are high, the flip-flop will remain in its previous state. Setting both  $\overline{R}$  and  $\overline{S}$  low simultaneously is forbidden since this forces both Q and  $\overline{Q}$  high.

Example 8.2

Show how to convert the  $\overline{R}\overline{S}$  flip-flop in Fig. 8.7 into an RS flip-flop.

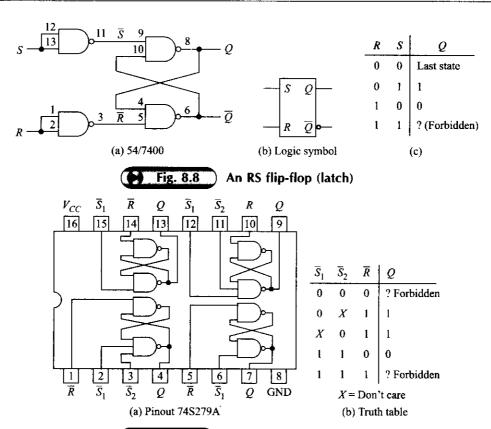

Solution By placing an inverter at each input as shown in Fig. 8.8, the 2 inputs are now R and S, and the resulting circuit behaves exactly as the RS flip-flop in Fig. 8.6. A single 54/7400 (quad 2-input NAND gate) is used.

Simple latches as discussed in this section can be constructed from NAND or NOR gates or obtained as medium-scale integrated circuits (MSI). For instance, the 74LS279 is a quad  $\overline{RS}$  latch. The pinout and truth table for this circuit are given in Fig. 8.9. Study the truth table carefully, and you will see that the latches behave exactly like the  $\overline{RS}$  flip-flop discussed above.

### Fig. 8.9

### **Quad SET-RESET latch**

The NOR-gate flip-flop in Fig. 8.3 is seen to be an active-high circuit because an H=1 at either the S or R input is required to change the output Q. On the other hand, the NAND-gate flip-flop in Fig. 8.7 can be considered an active-low circuit because an L=0 at either input is required to change Q. The NAND gates in Fig. 8.7 can be changed to bubbled-input OR gates as shown in Fig. 8.10. This circuit is equivalent to the NAND-gate latch in Fig. 8.7 and functions in exactly the same way. However, the bubbled inputs more clearly express circuit operation.

Fig. 8.10

**Bubbled OR-gate equivalent of** Fig. 8.7

- 1. What do the letters R and S stand for in the term "RS latch"?

- 2. A 74LS279 is a quad latch. What does quad mean?

- 3. Why is the NAND-gate latch considered active-low?

### 8.2 GATED FLIP-FLOPS

Two different methods for constructing an RS flip-flop were discussed in Sec. 8.1. The NOR-gate realization in Fig. 8.3b is an exact equivalent of the NAND-gate realization in Fig. 8.8a, and they both have the exact same symbol and truth table as given in Fig. 8.6. Both of these RS flip-flops, or latches, are said to be transparent; that is, any change in input information at R or S is transmitted immediately to the output at Q and  $\overline{Q}$  according to the truth table.

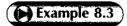

### Clocked RS Flip-Flops

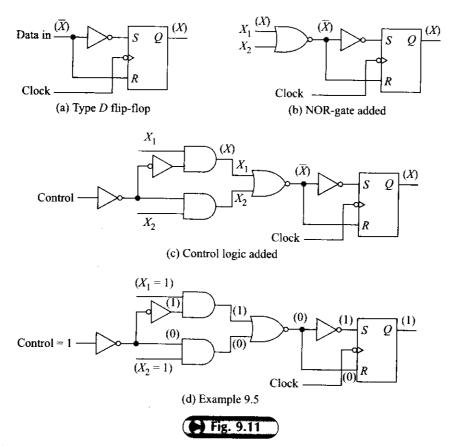

The addition of two AND gates at the R and S inputs as shown in Fig. 8.11 will result in a flip-flop that can be enabled or disabled. When the ENABLE input is low, the AND gate outputs must both be low and changes in neither R nor S will have any effect on the flip-flop output Q. The latch is said to be disabled.

When the ENABLE input is high, information at the R and S inputs will be transmitted directly to the outputs. The latch is said to be *enabled*. The output will change in response to input changes as long as the ENABLE is high. When the ENABLE input goes low, the output will retain the information that was present on the input when the high-to-low transition took place.

In this fashion, it is possible to *strobe* or *clock* the flip-flop in order to store information (set it or reset it) at any time, and then hold the stored information for any desired period of time. This flip-flop is called a *gated* or *clocked RS flip-flop*. The proper symbol and truth table are given in Fig. 8.11b. Notice that there are now three inputs—R, S, and the ENABLE or CLOCK input, labeled EN. Notice also that the truth-table output is not simply Q, but  $Q_{n+1}$ . This is because we must consider two different instants in time: the time before the ENABLE goes low  $Q_n$  and the time just after ENABLE goes low  $Q_{n+1}$ . When EN = 0, the flip-flop is disabled and R and S have no effect; thus the truth table entry for R and S is X (don't care).

Explain the meaning of  $Q_n$  the truth table in Fig. 8.11b.

Solution For the flip-flop to operate properly, there must be a PT on the EN input. While EN is high, the information on R and S causes the latch to set or reset. Then when EN transitions back to low, this information is retained in the latch. When this NT occurred, both R and S inputs were low (0), and thus there was no change of state. In other words, the value of Q at time n+1 is the same as it was at time n. Remember that time n occurs just before the NT on EN, and time n+1, occurs just after the transition.

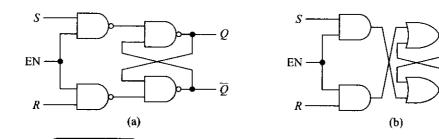

The logic diagrams shown in Fig. 8.12a and b illustrate two different methods for realizing a clock RS flip-flop. Both realizations are widely used in medium- and large-scale integrated circuits, and you will find them easy to recognize. You might like to examine the logic diagrams for a 54LS109 or a 54LS74, for instance.

Example 8.4

Fig. 8.12

the output waveform Q.

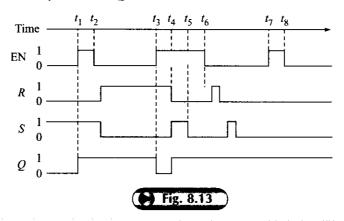

Figure 8.13 shows the input waveforms R, S, and EN applied to a clocked RS flip-flop. Explain

Two different realizations for a clocked RS flip-flop

Solution Between  $t_2$  and  $t_3$  both R and S change states, but since EN is low, the flip-flop is still disabled and Q remains at 1.

Between  $t_3$  and  $t_6$ , the flip-flop will respond to any change in R and S since EN is high. Thus at  $t_3$  Q goes low, and at  $t_4$  it goes back high. No change occurs at  $t_5$ . At  $t_6$  the value Q = 1 is latched and no changes in Q occur between  $t_6$  and  $t_7$  even though both R and S change.

Between  $t_7$ , and  $t_8$  no change in Q occurs since both R and S are low. Initially, the flip-flop is reset (Q = 0). At time  $t_1$  EN goes high; the flip-flop is now enabled, and it is immediately set (Q = 1) since R = 0 and S = 1. At time  $t_2$  EN goes low and the flip-flop is disabled and latches in the stable state Q = 1.

### Clocked D Flip-Flops

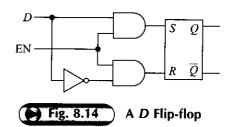

The RS flip-flop has two data inputs, R and S. To store a high bit, you need a high S; to store a low bit, you need a high R. Generation of two signals to drive a flip-flop is a disadvantage in many applications. Furthermore, the forbidden condition of both R and S high may occur inadvertently. This has led to the D flip-flop, a circuit that needs only a single data input.

Figure 8.14 shows a simple way to build a D (Data) flip-flop. This flip-flop is disabled when EN is low, but is *transparent* when EN is high. The action of the circuit is straightforward, as follows. When EN is low, both AND gates are disabled; therefore, D can change value without affecting the value of Q. On the other hand,

when EN is high, both AND gates are enabled. In this case, Q is forced to equal the value of D. When EN again goes low, Q retains or stores the last value of D.

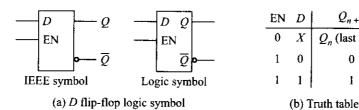

There are many ways to design D flip-flops. In general, a D flip-flop is a bistable circuit whose D input is transferred to the output when EN is high. Figure 8.15 shows the logic symbols used for any type of D flip-flop.

In this section we're talking about the kind of D flip-flop in

which Q can follow the value of D while EN is high. In other words, if the data bit changes while EN is high, the last value of D before EN return low is the value of D that is stored. This kind of D flip-flop is often called a D latch.

Figure 8.15b shows the truth table for a D latch. While (EN) is low, D is a don't care (X); Q will remain latched in its last state. When EN is high, Q takes on the last value of D. If D is changing while EN is high, it is the last value of D that is stored.

# Fig. 8.15 D Flip-flo

### D Flip-flop logic symbol

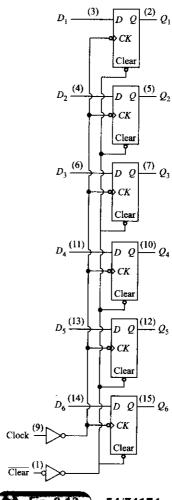

The idea of data storage is illustrated in Fig. 8.16. Four D latches are driven by the same clock signal. When the clock goes high, input data is loaded into the flip-flops and appears at the output. Then when the clock goes low, the output retains the data. For instance, suppose that the data input is

$$D_3D_2D_1D_0 = 0111$$

When the clock goes high, this word is loaded into the D latches, resulting in an output of

$$Q_3Q_2Q_1Q_0 = 0111$$

After the clock goes low, the output data is retained,

$D_3$   $D_2$   $D_1$   $D_0$   $D_0$

or stored. As long as the clock is low, the D values can change without affecting the Q values.

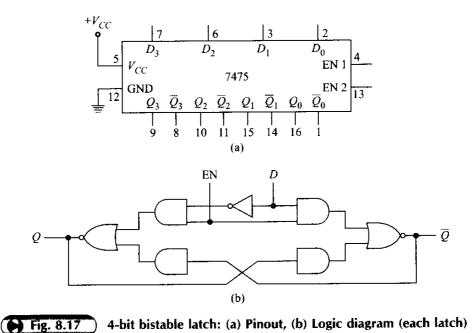

The 7475 in Fig. 8.17 is a TTL MSI circuit that contains four *D* latches; it's called a *quad bistable latch*. The 7475 is ideal for handling 4-bit nibbles of data. If more than one 7475 is used, words of any length can be stored.

- 4. What does an entry X mean in a flip-flop truth table?

- 5. What could you do to disable the flip-flop in Fig. 8.11?

- 6. Which flip-flop is easier to use, the RS of the D, as a clocked or gated latch to store data?

8.3 EDGE-TRIGGERED RS FLIP-FLOPS

The simple latch-type flip-flops presented in Sec. 8.1 are completely transparent; that is, the output Q immediately follows any change of state at the input (R, S, or D). The gated or clocked RS and D flip-flops in Sec. 8.2 might be considered semitransparent. That is, the output Q will change state immediately provided that the EN input is high. If any of these flip-flops are used in a synchronous system, care must be taken to ensure that all flip-flop inputs change state in synchronism with the clock. One way of resolving the problem for gated flip-flops is to allow changes in R, S, and D input levels only when EN is low (or require fixed levels at R, S, and D any time EN is high). At the very least, these are highly inconvenient restrictions, and at the worst they may in fact be impossible to realize. From the previous chapter, we know that virtually all digital systems operate in a synchronous mode. Thus the edge-triggered flip-flop was developed to overcome these rather severe restrictions.

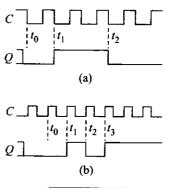

### Positive-Edge-Triggered RS Flip-Flops

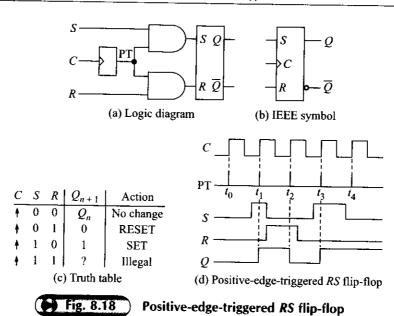

In Fig. 8.18a, the clock (C) is applied to a positive pulse-forming circuit (discussed in Sec. 7.1). The PTs developed are then applied to a gated RS flip-flop. The result is a positive-edge-triggered RS flip-flop, with the IEEE symbol given in Fig. 8.18b. The small triangle inside the symbol (dynamic input indicator) indicates that Q can change state only with PTs of the clock (C). Each PT of the clock in Fig. 8.18c produces a very narrow PT that is applied to the AND gates. The AND gates are active only while the PT is high (perhaps 25 ns), and thus Q can change state only during this short time period. In this manner Q changes state in synchronism with the PTs of the clock.

This flip-flop is easy to use in any synchronous system! Another way of expressing its behavior is to say the flip-flop is transparent only during PTs; it is not transparent for the remainder of the time. In other words, S and R inputs affect Q only while the positive pulse is high, and they need to be static only during this very short time.

The truth table for the edge-triggered RS flip-flop is given in Fig. 8.18c. The small vertical arrows under C (clock) mean that changes of state (Q) occur according to the R and S levels, but only during PTs of the clock. Look at the waveforms in Fig. 8.18d. Note that when Q changes state, it does so in exact synchronism with PTs of the clock C.

# Example 8.5

Use the positive-edge-triggered RS flip-flop truth table to explain Q changes of state with time in Fig. 8.18d.

Solution Here's what happens at each point in time:

Time  $t_0$ : S = 0, R = 0, no change in Q(Q remains 0)

Time  $t_1$ : S = 1, R = 0, Q changes from 0 to 1

Time  $t_2$ : S = 0, R = 1, Q resets to 0

Time  $t_3$ : S = 1, R = 0, Q sets to 1

Time  $t_4$ : S = 0, R = 0, no change in Q(Q remains 1)

Notice that either R or S, or both, are allowed to change state at any time, whether C is high or low. The only time both R and S must be stable (unchanging) is during the short PTs of the clock.

### Negative-Edge-Triggered RS Flip-Flops

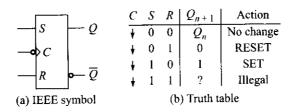

The symbol in Fig. 8.19a is for a negative-edge-triggered RS flip-flop. The truth table in Fig. 8.19b shows that Q changes state according to the R and S inputs, but only during NTs of the clock. On the IEEE symbol, the small bubble on the clock input (C) means active-low. This bubble, along with the dynamic input indicator,

Fig. 8.19 Ne

Negative-edge-triggered RS flip-flop

means negative-edge triggering. This flip-flop behaves exactly like the positive-edge-triggered RS flip-flop, except that changes in output Q are synchronized with NTs of the clock (C).

Example 8.6

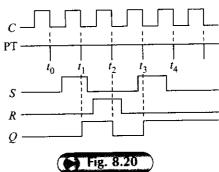

Use the negative-edge-triggered RS flip-flop truth table to explain Q changes of state with time in Fig. 8.20.

Solution Here's what happens at each point in time:

Time  $t_0$ : S = 0, R = 0, no change in Q(Q remains 0)

Time  $t_1$ : S = 1, R = 0, Q changes from 0 to 1

Time  $t_2$ : S = 0, R = 1, Q resets to 0

Time  $t_3$ : S = 1, R = 0, Q sets to 1

Time  $t_4$ : S = 0, R = 0, no change in Q(Q remains 1)

Notice that either R or S, or both, are allowed to change state at any time, whether C is high or low. The only time both R and S must be stable (unchanging) is during the short NTs of the clock.

- 7. What does it mean to say that a flip-flop is transparent?

- 8. What is positive-edge triggering?

- 9. How does an RS latch differ from an edge-triggered RS flip-flop?

### 8.4 EDGE-TRIGGERED D FLIP-FLOPS

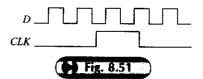

Although the D latch is used for temporary storage in electronic instruments, an even more popular kind of D flip-flop is used in digital computers and systems. This kind of flip-flop samples the data bit at a unique point in time.

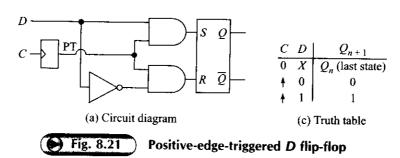

Figure 8.21 shows a positive pulse-forming circuit at the input of a D latch. The narrow positive pulse (PT) enables the AND gates for an instant. The effect is to activate the AND gates during the PT of C, which is equivalent to sampling the value of D for an instant. At this unique point in time, D and its complement hit the flip-flop inputs, forcing Q to set or reset (unless Q already equals D). Again, this operation is called edge triggering because the flip-flop responds only when the clock is in transition between its two voltage states. The triggering in Fig. 8.21 occurs on the positive-going edge of the clock; this is why it's referred to as positive-edge triggering.

The truth table in Fig. 8.21b summarizes the action of a positive-edge-triggered D flip-flop. When the clock is low, D is a don't care and Q is latched in its last state. On the leading edge of the clock (PT), designated by the up arrow, the data bit is loaded into the flip-flop and Q takes on the value of D.

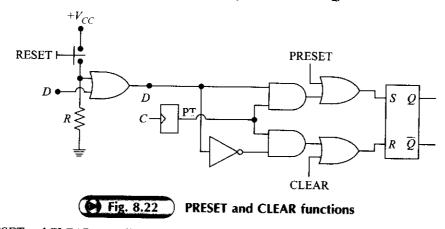

When power is first applied, flip-flops come up in random states. To get some computers started, an operator has to push a RESET button. This sends a CLEAR or RESET signal to all flip-flops. Also, it's necessary in some digital systems to preset (synonymous with set) certain flip-flops.

Figure 8.22 shows how to include both functions in a D flip-flop. The edge triggering is the same as previously described. Depressing the RESET button will set Q to 1 with the first PT of the clock. Q will remain high as long as the button is held closed. The first PT of the clock after releasing the button will set Q according to the D input. Furthermore, the OR gates allow us to slip in a high PRESET or a high CLEAR when desired. A high PRESET forces Q to equal 1; a high CLEAR resets Q to 0.

The PRESET and CLEAR are called *asynchronous inputs* because they activate the flip-flop independently of the clock. On the other hand, the *D* input is a synchronous input because it has an effect only with PTs of the clock.

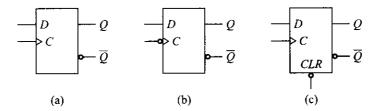

Figure 8.23a is the IEEE symbol for a positive-edge-triggered D flip-flop. The clock input has a small triangle to serve as a reminder of edge triggering. When you see this symbol, remember what it means; the D input is sampled and stored on PTs of the clock.

Sometimes, triggering on NTs of the clock is better suited to the application. In this case, an internal inverter can complement the clock pulse before it reaches the AND gates. Figure 8.23b is the symbol for a negative-edge-triggered D flip-flop. The bubble and triangle symbolize the negative-edge triggering.

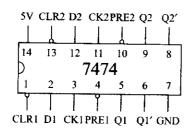

Figure 8.23c is another commercially available D flip-flop (the 54/74175 or 54/74LS175). Besides having positive-edge triggering, it has an inverted CLEAR input This means that a low CLR resets it. The 54/74175 has four of these D flip-flops in a single 16-pin dual in-line package (DIP), and it's referred to as a quad D-type flip-flop with clear.

Fig. 8.23

Dflip-flopsymbols: (a) Positive-edge-triggered, (b) Negative-edge-triggered, (c) Positive-edge-triggered with active low clear

- 10. The C input to the D flip-flop in Fig. 8.21 is held low. What effect does the D input have?

- 11. To preset the flip-flop in Fig. 8.22, what level is required at the preset input. What is the resulting state of Q?

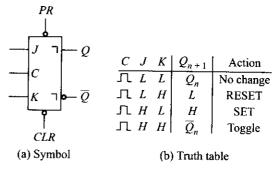

### 8.5 EDGE-TRIGGERED JK FLIP-FLOPS

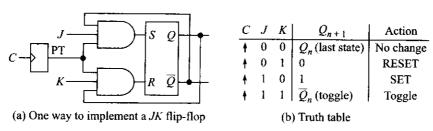

Setting R = S = 1 with an edge-triggered RS flip-flop forces both Q and  $\overline{Q}$  to the same logic level. This is an illegal condition, and it is not possible to predict the final state of Q. The JK flip-flop accounts for this illegal input, and is therefore a more versatile circuit. Among other things, flip-flops can be used to build counters. Counters can be used to count the number of PTs or NTs of a clock. For purposes of counting, the JK flip-flop is the ideal element to use. There are many commercially available edge-triggered JK flip-flops. Let's see how they function.

### Positive-Edge-Triggered JK Flip-Flops

In Fig. 8.24, the pulse-forming box changes the clock into a series of positive pulses, and thus this circuit will be sensitive to PTs of the clock. The basic circuit is identical to the previous positive-edge-triggered RS flip-flop, with two important additions:

- 1. The Q output is connected back to the input of the lower AND gate.

- 2. The  $\overline{Q}$  output is connected back to the input of the upper AND gate.

This cross-coupling from outputs to input schanges the RS flip-flop into a JK flip-flop. The previous S input is now labeled J, and the previous R input is labeled K. Here's how it works:

- 1. When J and K are both low, both AND gates are disabled. Therefore, clock pulses have no effect. This first possibility is the initial entry in the truth table. As shown, when J and K are both 0s, Q retains its last value.

- 2. When J is low and K is high, the upper gate is disabled, so there's no way to set the flip-flop. The only possibility is reset. When Q is high, the lower gate passes a RESET pulse as soon as the next positive

### Fig. 8.24 A positive-edge-triggered JK flip-flop

clock edge arrives. This forces Q to become low (the second entry in the truth table). Therefore, J = 0 and K = 1 means that the next PT of the clock resets the flip-flop (unless Q is already reset).

- 3. When J is high and K is low, the lower gate is disabled, so it's impossible to reset the flip-flop. But you can set the flip flop as follows. When Q is low,  $\overline{Q}$  is high; therefore, the upper gate passes a SET pulse on the next positive clock edge. This drives Q into the high state (the third entry in the truth table). As you can see, J=1 and K=0 means that the next PT of the clock sets the flip-flop (unless Q is already high).

- 4. When J and K are both high (notice that this is the forbidden state with an RS flip-flop), it's possible to set or reset the flip-flop. If Q is high, the lower gate passes a RESET pulse on the next PT. On the other hand, when Q is low, the upper gate passes a SET pulse on the next PT. Either way, Q changes to the complement of the last state (see the truth table). Therefore, J=1 and K=1 mean the flip-flop will toggle (switch to the opposite state) on the next positive clock edge.

Propagation delay prevents the JK flip-flop from racing (toggling more than once during a positive clock edge). Here's why. In Fig. 8.24, the outputs change after the PT of the clock. By then, the new Q and  $\overline{Q}$  values are too late to coincide with the PTs driving the AND gates. For instance, if  $t_p = 20$  ns, the outputs change approximately 20 ns after the leading edge of the clock. If the PTs are narrower than 20 ns, the returning Q and  $\overline{Q}$  arrive too late to cause false triggering.

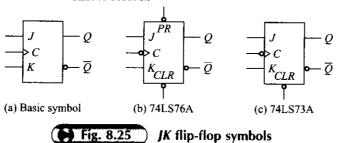

Figure 8.25a shows a symbol for a JK flip-flop of any design. When you see this on a schematic diagram, remember that on the next PT of the clock:

- 1. J and K low: no change of O.

- 2. J low and K high: Q is reset low.

- 3. J high and K low: Q is set high.

- 4. J and K both high: Q toggles to opposite state.

You can include OR gates in the design to accommodate PRESET and CLEAR as was done earlier. Figure 8.25b gives the symbol for a *JK* flip-flop with *PR* and *CLR*. Notice that it is negative-edge-triggered and requires a low *PR* to set it or a low *CLR* to reset it.

Figure 8.25c is another commercially available JK flip-flop. It is negative-edge-triggered and requires a low CLR to reset it. The output Q reacts immediately to a PR or CLR signal. Both PR and CLR are asynchronous, and they override all other input signals.

Toggle flip-flop, popularly known as T flip-flop has following input-output relation. When input T = 0, the output Q does not change its state. For T = 1, the output Q toggles its value. Derive T flip-flop from JK flip-flop.

Solution From Fig. 8.24b we find for input J = K = 0, the output  $Q_{n+1} = Q_n$ , i.e. output does not change its state. And for J = K = 1, the output  $Q_{n+1} = Q'_n$ , i.e. output toggles. Thus, if we tie J and K inputs of JK flip-flop together and make a common input T = J = K, the resulting circuit will behave as T flip-flop.

- 12. What is the primary difference between a JK and an RS flip-flop?

- 13. How could you change an edge-triggered RS flip-flop into an edge-triggered JK flip-flop?

### 8.6 FLIP-FLOP TIMING

Diodes and transistors cannot switch states immediately. It always takes a small amount of time to turn a diode on or off. Likewise, it takes time for a transistor to switch from saturation to cutoff, and vice versa. For bipolar diodes and transistors, the switching time is in the nanosecond region.

Switching time is the main cause of propagation delay, designated  $t_p$ . This represents the amount of time it takes for the output of a gate or flip-flop to change states after the input changes. For instance, if the data sheet of an edge-triggered D flip-flop lists  $t_p = 10$  ns, it takes about 10 ns for Q to change states after D has been sampled by the clock edge. This propagation delay time has been used to construct the "pulse-forming circuit" used with edge-triggered flip-flops. When flip-flops are used to construct counters, the propagation delay is often small enough to be ignored.

Stray capacitance at the D input (plus other factors) makes it necessary for data bit D to be at the input before the clock edge arrives. The setup time  $t_{\text{setup}}$  is the minimum amount of time that the data bit must be present before the clock edge hits. For instance, if a D flip-flop has a setup time of 15 ns, the data bit to be stored must be at the D input at least 15 ns before the clock edge arrives; otherwise, the manufacturer does not guarantee correct sampling and storing.

Furthermore, data bit D has to be held long enough for the internal transistors to switch states. Only after the transition is assured can we allow data bit D to change. Hold time  $t_{hold}$  is the minimum amount of time that data bit D must be present after the PT of the clock. For example, if  $t_{setup} = 15$  ns and  $t_{hold} = 5$  ns, the data bit has to be at the D input at least 15 ns before the clock edge arrives and held at least 5 ns after the clock PT.

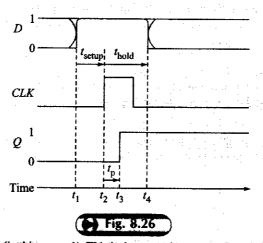

Typical waveforms for setting a 1 in a positive-edge-triggered flip-flop are shown in Fig. 8.26. Discuss the timing.

Solution The lower line in Fig. 8.26 is the time line with critical times marked on it. Prior to  $t_1$ , the data can be a 1 or a 0, or can be changing. This is shown by drawing lines for both high and low levels on D. From time  $t_1$  to  $t_2$ , the

data line D must be held steady (in this case a 1). This is the setup time  $t_{\text{Setup}}$ . Data is shifted into the flip-flop at time  $t_2$  but does not appear at Q until time  $t_3$ . The time from  $t_2$  to  $t_3$  is the propagation time  $t_p$ . In order to guarantee proper operation, the data line must be held steady from time  $t_2$  until  $t_4$ ; this is the hold time  $t_{\text{hold}}$ . After  $t_4$ , D is free to change states—shown by the double lines.

### 8.7 EDGE TRIGGERING THROUGH INPUT LOCK OUT

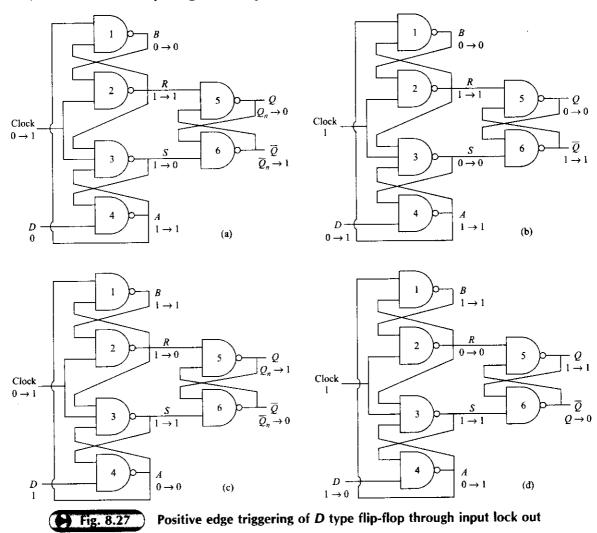

We have seen how edge triggering of flip-flops can be achieved by pulse forming circuit (Section 7.1). This requires application of a very narrow pulse which is generated using differential propagation delays of two signal flow paths while the flip-flops themselves are level triggered. An alternate way of achieving edge triggering is to implement a kind of lock out of the input so that it is not able to enforce a change at output which itself is level triggered. This is to say that the effect of change in input is allowed only at the edge and not after the edge. Let us see how this is possible by implementing a positive edge triggered D type flip-flop. This requires three NAND latches as shown in Fig. 8.27 with one NAND gate (number 3) having three inputs and the rest are all two input NAND gates. Note that for a NAND gate output to be 0, all the inputs must be at 1, else the output is 1. The output latch behaves like an SR flip flop where no change in output occurs if S = 1, R = 1.

Now, if the clock input is held at 0 then irrespective of what is present at D input, the NAND logic makes both S=1, R=1 and thus there could be no change in the output. If Clock = 1 then SR can always change if other inputs of NAND gates 2 and 3 change and thus the output is essentially level triggered. We will now explain how input lock out makes the circuit as a whole a positive edge triggered circuit.

Consider the case when Clock = 0 and D = 0 (Fig. 8.27a). Since, for a NAND gate, 0 is the forcing input, the intermediate outputs are S = 1, R = 1 and A = 1 which make B = 0. Now, clock makes a transition from  $0 \to 1$ . D = 0 forces A = 1 and B = 0 keeps R = 1. Thus, after this transition, S = 0, R = 1, A = 1 and B = 0. This makes Q = 0 irrespective of the previous state and one can see that the value at D, i.e. 0 is transferred to Q after the clock trigger. Next, we see if at Clock = 1, D is changed, then whether Q is changed. This is shown in Fig. 8.27b as a follow-up of Fig. 8.27a. Before D makes a transition Clock = 1, D = 0 and intermediate outputs S = 0, R = 1, A = 1, B = 0 and Q = 0. When D goes to 1, A<sup>th</sup> NAND gate is only directly affected as D is not connected elsewhere. However, the output A of this gate does not change as it is kept held at 1 by the

other input coming from S = 0. Thus, S = 0, R = 1, A = 1, B = 0 and Q = 0. This is the lock out of input we were referring to. Note that clock going from 1 to 0 does not change Q as that transition makes S = 1, R = 1.

Next, consider the case when Clock = 0 and D = 1. This is shown in Fig. 8.27c. S = 1, D = 1 make A = 0 which in turn makes B = 1. Now, clock makes a transition from  $0 \to 1$ . A = 0 maintains S = 1. Both the inputs of  $2^{\text{nd}}$  NAND gate being 1, R = 0. S = 1, R = 0 make Q = 1 irrespective of previous state and thus after positive clock trigger, the logic value of D arrives at Q for D = 1 case, too. With Clock = 1, if input D changes from 1 to 0, will the output Q change? This  $4^{\text{th}}$  possibility is shown in Fig. 8.27d. D = 0 makes A = 1 but R = 0 maintains B = 1 and S = 1. Thus, after the transition, SR remains at where it was and input D remaines locked out, i.e. unable to effect any change in the output at Clock = 1.

### 8.8 JK MASTER-SLAVE FLIP-FLOPS

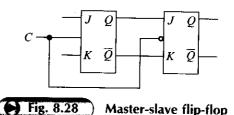

Figure 8.28 shows one way to build a JK master-slave flip-flop. Here's how it works.

1. To begin with, the master is positive-level-triggered and the slave is negative-level-triggered. Therefore, the master responds to its J and K inputs before the slave. If J=1 and K=0, the master sets on the positive clock transition. The high Q output of the master drives the J input of the slave, so on the negative clock transition, the slave sets, copying the action of the master.

2. If J = 0 and K = 1, the master resets on the PT of the clock. The high  $\overline{Q}$  output of the master goes to the K input of the slave. Therefore, the NT of the clock forces the slave to reset. Again, the slave has copied the master.

3. If the master's J and K inputs are both high, it toggles on the PT of the clock and the slave then toggles on the clock NT. Regardless of what the master does, therefore, the slave copies it: if the master sets, the slave sets; if the master resets, the slave resets.

4. If J = K = 0, the flip-flop is disabled and Q remains unchanged.

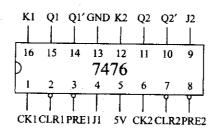

The symbol for a 7476 master-slave flip-flop is shown in Fig. 8.29. Either it can be preset to Q = H by taking PR low, or it can be reset to Q = L by taking CLR low. These two inputs take precedence over all other signals!

There is something different however. First of all, notice that the clock (C) is not edge-triggered. The master does in fact change state when C goes high. However, while the clock is high, any change in J or K will immediately affect the master flip-flop. In other words, the master is transparent while the clock is high, and thus J and K must be static during this time.

Fig. 8.29 7476 JK master flip-flop.

The truth table in Fig. 8.29b reveals this action by means of the pulse symbol (\_\_\_).

Second, the symbol  $\ \$  appearing next to the  $\ Q$  and the  $\ \overline{Q}$  outputs is the IEEE designation for a postponed output. In this case, it means  $\ Q$  does not change state until the clock makes an NT. In other words, the contents of the master are shifting into the slave on the clock NT, and at this time  $\ Q$  changes state.

To summarize: The master is set according to J and K while the clock is high; the contents of the master are then shifted into the slave (Q changes state) when the clock goes low. This particular flip-flop might be referred to as *pulse-triggered*, to distinguish it from the edge-triggered flip-flops previously discussed.

There are numerous pulse-triggered master-slave flip-flops in use today. However, because edge-triggered flip-flops have overcome the restriction of holding J and K static when the clock is high, most new designs incorporate edge-triggered devices. Some of the more popular pulse-triggered flip-flops you might encounter include the 7473, 7476, and 7478. Their more modern, edge-triggered counterparts include the 74LS73A, the 74LS76A, and the 74LS78A.

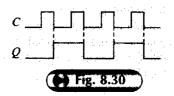

The JK master-slave flip-flop in Fig. 8.29 has its J and K inputs tied to  $+V_{CC}$  and a series of pulses (actually a square wave) are applied to its C input. Describe the waveform at Q.

Solution Since J = K = 1, the flip-flop simply toggles each time the clock goes low. The wave-form at Q has a period twice that of the C waveform. In other words, the frequency of Q is only one-half that of C. This circuit acts as a frequency divider—the output frequency is equal to the input frequency divided by 2. Note that Q changes state on NTs of the clock. The waveforms are given in Fig. 8.30.

- 14. What is the main difference between an edge-triggered and a pulse-triggered JK flip-flop?

- 15. Explain the operation of the master-slave flip-flop in Fig. 8.29.

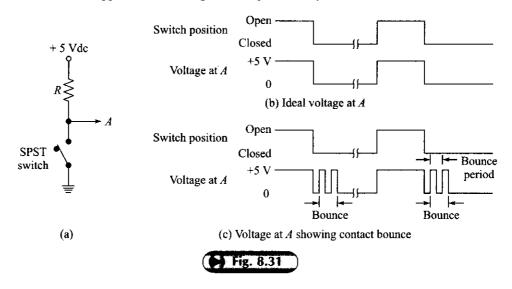

### 8.9 SWITCH CONTACT BOUNCE CIRCUITS

In nearly every digital system there will be occasion to use mechanical contacts for the purpose of conveying an electrical signal; examples of this are the switches used on the keyboard of a computer system. In each case, the intent is to apply a high logic level (usually +5 Vdc) or a low logic level (0 Vdc). The single-pole—single-throw (SPST) switch shown in Fig. 8.31a is one such example. When the switch is open, the voltage at point A is +5 Vdc; when the switch is closed, the voltage at paint A is 0 Vdc. Ideally, the voltage waveform at A should appear as shown in Fig. 8.31b as the switch is moved from open to closed, or vice versa.

In actuality, the waveform at point A will appear more or less as shown in Fig. 8.31c, as the result of a phenomenon known as *contact bounce*. Any mechanical switching device consists of a moving contact arm restrained by some sort of a spring system. As a result, when the arm is moved from one stable position to the other, the arm bounces, much as a hard ball bounces when dropped on a hard surface. The number of bounces that occur and the period of the bounce differ for each switching device. Notice carefully that in this particular instance, even though actual physical contact bounce occurs each time the switch is opened or closed, contact bounce appears in the voltage level at point A only when the switch is closed.

If the voltage at point A is applied to the input of a TTL circuit, the circuit will respond properly when the switch is opened, since no contact bounce occurs. However, when the switch is closed, the circuit will respond as if multiple signals were applied, rather than the single-switch closure intended—the undesired result of mechanical contact bounce. There is a need here for some sort of electronic circuit to eliminate the contact bounce problem.

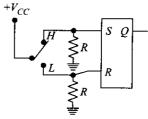

### A Simple RS Latch Debounce Circuit

The RS latch in Fig. 8.32 will remove any contact bounce due to the switch. The output (Q) is used to generate the desired switch signal.

When the switch is moved to position H, R=0 and S=1. Bouncing occurs at the S input due to the switch. The flip-flop "sees" this as a series of high and low inputs, settling with a high level. The flip-flop will immediately be set with Q=1 at the first high level on S. When the switch bounces, losing contact, the input signals are R=S=0, therefore the flip-flop remains set (Q=1). When the switch regains contact, R=0 and S=1; this causes an attempt to again set the flip-flop. But since the flip-flop is already set, no changes occur at Q. The result is that the flip-flop responds to the first, and only to the first, high level at its S input, resulting in a "clean" low-to-high signal at its output (Q).

When the switch is moved to position L, S=0 and R=1. Bouncing occurs at the R input due to the switch. Again, the flip-flop "sees" this as a series of high and low inputs. It simply

(a) Switch contact bounce eliminator

(b) Switch bounce

Debounce circuit

responds to the *first* high level, and ignores all following transitions. The result is a "clean" high-to-low signal at the flip-flop output. The waveforms in Fig. 8.32b illustrate the behavior.

- 16. What is switch contact bounce?

- 17. Why is switch contact bounce important to account for in a digital system?

### 8.10 VARIOUS REPRESENTATIONS OF FLIP-FLOPS

There are various ways a flip-flop can be represented, each one suitable for certain application. Considering basic flip-flop truth table as starting point, this section derives these representations.

### **Characteristic Equations of Flip-flops**

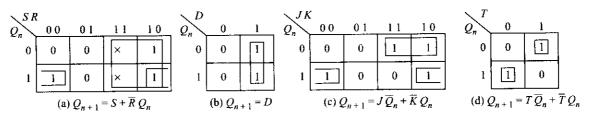

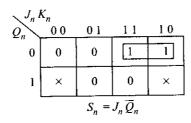

The characteristic equations of flip-flops are useful in analyzing circuits made of them. Here, next output  $Q_{n+1}$  is expressed as a function of present output  $Q_n$  and input to flip-flops. Karnaugh Map can be used to get the optimized expression and truth table of each flip-flop is mapped into it. This is shown in Fig. 8.33 for all types of flip-flops. The logic equations are presented in SOP form by forming largest group of 1's for each

Fig. 8.33

Characteristic equations of (a) SR flip-flop, (b) D flip-flop, (c) JK flipflop, (d) T flip-flop

flip-flop. For SR flip-flop, since S = R = 1 input is not allowed we have don't care states in corresponding locations in Karnaugh Map. This means, it does not matter if  $Q_{n+1}$  is 0 or 1 if SR = 11 as such a combination at input side will never arise.

The equation for SR flip-flop and all others thus can be represented in a summarized form as

$Q_{n+1} = S + R'Q_n$ SR flip-flop: JK flip-flop:

D flip-flop:

$Q_{n+1} = JQ_n' + K'Q_n$   $Q_{n+1} = D$   $Q_{n+1} = TQ_n' + T'Q_n$ T flip-flop:

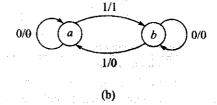

### Flip-Flops as Finite State Machine

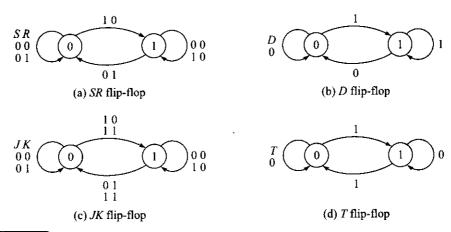

In a sequential logic circuit the value of all the memory elements at a given time define the state of that circuit at that time. Finite State Machine (FSM) concept offers a better alternative to truth table in understanding progress of sequential logic with time. For a complex circuit a truth table is difficult to read as its size becomes too large. In FSM, functional behavior of the circuit is explained using finite number of states. State transition diagram is a very convenient tool to describe an FSM. In Fig. 8.34 all the flip-flops are represented as finite state machine through their state transition diagrams.

Fig. 8.34

State transition diagram of (a) SR flip-flop, (b) D flip-flop, (c) JK flipflop, (d) T flip-flop

Let us see how state transition diagram for SR flip-flop is developed from its truth table or characteristic equation. Each flip-flop can be at either of 0 or 1 state defined by its stored value at any given time. Application of input may change the stored value, i.e. state of the flip-flop. This is shown by directional arrow and the corresponding input is written alongside. If SR flip-flop stores 0, then for SR = 00 or 01 the stored value does not change. For SR = 10, flip-flop output changes to 1. Note that, SR = 11 is not allowed in SR flip-flop. When SR flip-flop stores 1, application of SR = 00 or 10 does not change its value and only when SR = 01, output changes to 0. State transitions on application of all possible combination of inputs at every state are shown in Fig. 8.34(a) for SR flip-flop. The state transition diagrams are developed in a similar way for D, JK, T flip-flops and are shown in Figs. 8.34 (b), (c), (d) respectively. We see, the timing relation implicit in flip-flop truth tables are brought to the forefront by FSM concept and state transition diagram.

### Flip-Flop Excitation Table

In synthesis or design problem excitation tables are very useful and its importance is analogous to that of truth table in analysis problem. Excitation table of a flip-flop is looking at its truth table in a reverse way. Here, flip-flop input is presented as a dependent function of transition  $Q_n \rightarrow Q_{n+1}$  and comes later in the table. This

is derived from flip-flop truth table or characteristic equation but more directly from its state transition diagram. Figure 8.35 gives a summary presentation of excitation tables of all the flip-flops.

From Fig. 8.34(a), one can see if present state is 0 application of  $SR = 0 \times$  does not alter its value where 'x' denotes don't care condition in R input. State 0 to 1 transition occurs when SR = 10 is pres-

| L | $Q_n$       | $\rightarrow Q_{n+1}$ | S           | R           | $\overline{J}$ | K           | D           | T           |

|---|-------------|-----------------------|-------------|-------------|----------------|-------------|-------------|-------------|

|   | 0<br>0<br>1 | 0<br>1<br>0           | 0<br>1<br>0 | ×<br>0<br>1 | 0<br>1<br>×    | ×<br>×<br>1 | 0<br>1<br>0 | 0<br>1<br>1 |

| L | 1           | 1                     | ×           | 0_          | ×              | 0           | 1           | 0           |

Fig. 8.35

**Excitation table of flip-flops**

ent at the input side while state 1 to 0 transition occurs if SR = 01. Present state 1 is maintained if SR = 0, i.e. SR = 00 or SR = 01. This is shown in Fig. 8.35 along SR column. Excitation table for other flip-flops are obtained in a similar way.

Note that, JK flip-flop has maximum number of don't care 'x' conditions and D flip-flop input simply follows the value to which transition is made.

- 18. What is characteristic equation of a flip-flop?

- 19. What is a Finite State Machine?

- 20. How is excitation table different from flip-flop truth table?

A fictitious flip-flop with two inputs A and B functions like this. For AB = 00 and 11 the output becomes 0 and 1 respectively. For AB = 01, flip-flop retains previous output while output complements for AB = 10. Draw the truth table and excitation table of this flip-flop.

Solution The truth table and corresponding excitation tables are presented in Figs. 8.36(a) and (b) respectively. For  $0 \rightarrow 0$  transition we see AB need to be 00 or 01. Hence, we write  $AB = 0 \times$  in that place and similarly for other transitions.

| A   | В    | $Q_{n+1}$        |

|-----|------|------------------|

| 0   | 0    | 0                |

| . 0 | 1    | $Q_n$            |

| 1   | 0    | $\overline{Q}_n$ |

| - 1 | 1    | 1                |

| 12  | · (a | )                |

| $Q_n \to Q_{n+1}$ | Å | В |  |  |  |

|-------------------|---|---|--|--|--|

| $0 \rightarrow 0$ | 0 | × |  |  |  |

| 0 → 1             | 1 | × |  |  |  |

| 1 → 0             | × | 0 |  |  |  |

| 1 → 1             | × | 1 |  |  |  |

| (b)               |   |   |  |  |  |

Fig. 8.36

Solution for example 8.10: (a) Truth table, (b) Excitation table

### 8.11 ANALYSIS OF SEQUENTIAL CIRCUITS

A sequential logic circuit contains flip-flops as memory elements and may also contain logic gates as combinatorial circuit elements. Analysis of a circuit helps to explain its performance. We may use truth tables of each building block or corresponding equations for this purpose. In this section, we look at important issues in an analysis problem through an example. In subsequent chapters, more analysis examples will be taken up.

### Example 8.11

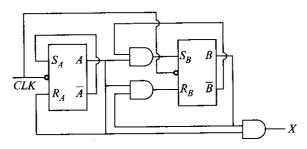

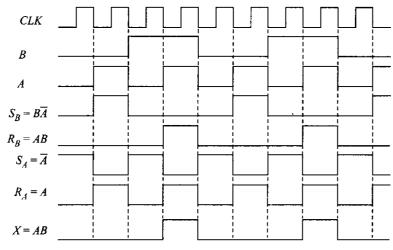

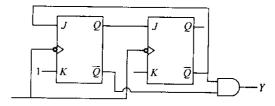

Consider, the sequential circuit shown in Fig. 8.37. It has only input CLK in the form of fixed frequency binary pulses that triggers both the flip-flops. An output X is generated from flip-flop outputs as shown. Analysis of this circuit will give how flip-flop values (or states) and more importantly output X change with input CLK. The steps are as follows.

## Fig. 8.37

A sequential logic circuit for analysis purpose

Note from the circuit diagram flip-flop input relations:  $S_A = A'_n$ ,  $R_A = A_n$  and  $S_B = A_n B'_n$ ,  $R_B = A_n B_n$ . Next, using characteristic equation of SR flip-flop (Section 8.9) we can write, for flip-flop A

$$A_{n+1} = S_A + R'_A A_n$$

=  $A'_n + A'_n A_n$  (Substituting  $S_A = A'_n$  and  $R_A = A_n$ )

=  $A'_n$

and for flip-flop B

$$B_{n+1} = S_B + R_B'B_n$$

=  $A_nB_n' + (A_nB_n)'B_n$  (Substituting  $S_B = A_nB_n'$  and  $R_B = A_nB_n$ )

=  $A_nB_n' + (A_n' + B_n')B_n$  (Following De Morgan's Theorem)

$$= A_n B_n' + A_n' B_n$$

$$= A_n \oplus B_n$$

Now the output from the given circuit,  $X_n = A_n B_n$

The equation shows that present (given by time index n) values of A and B flip-flop, also called *states* of the sequential circuit determine present output and next (given by time index n+1) flip-flop values or state of the circuit. Thus, if present state is  $B_n=0$ ,  $A_n=0$  then present output  $X_n=A_nB_n=0.0=0$  and at the end of first clock cycle we get next state is  $B_{n+1}=0\oplus 0=0$ ,  $A_{n+1}=0'=1$ . In next clock cycle present state is nothing but next state of previous cycle or  $B_n=0$ ,  $A_n=1$ . The output now is generated as  $X_n=0.1=0$  and next state is determined as  $B_{n+1}=0\oplus 1=1$ ,  $A_{n+1}=1'=0$ . Continuing this exercise we arrive at *state analysis table* also called state table as shown in Table 8.1.

## Table 8.1 State Analysis Table for Analysis Example

|       | esent<br>tate | Present Input    |                 |              | Next S      | Present<br>Output          |                  |               |

|-------|---------------|------------------|-----------------|--------------|-------------|----------------------------|------------------|---------------|

| $B_n$ | $A_n$         | $S_B = A_n B_n'$ | $R_B = A_n B_n$ | $S_A = A_n'$ | $R_B = A_n$ | $B_{n+1} = A_n \oplus B_n$ | $A_{n+1} = A_n'$ | $X = A_n B_n$ |

| 0     | 0             | 0                | 0               | 1            | 0           | 0                          | 1                | 0             |

| 0     | 1             | 1                | 0               | 0            | 1           | 1                          | Ô                | Õ             |

| 1     | 0             | 0                | 0               | 1            | 0           | 1                          | .1               | Õ             |

| 1     | 1             | 0                | 1               | 0            | 1           | o ·                        | Ô                | i             |

| 0     | 0             | 0                | 0               | 1            | 0           | Õ                          | ĭ                | ò             |

| 0     | 1             | ***              | ***             |              |             |                            | •••              | Repeats       |

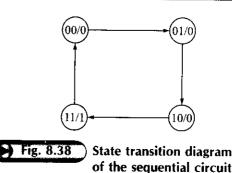

We find that the states as well as output of the above circuit repeat after every four clocking periods and at every fourth clock period the output remains 1 for one clock period. The circuit thus behaves like a counter that counts number of clock pulses that has arrived at its input and signals when there is a count of four. A pictorial presentation of the performance of the circuit showing state transitions with each clock is shown in Fig. 8.38. The values within the circle follow syntax:  $B_nA_n/X_n$ . Flip-flop outputs defining current state is shown to the left of '/' and current output appears at right. Such circuit where output is directly derived from current state

given in Fig. 8.37

only and not from current inputs are called Moore circuit. If current inputs are also used in output forming logic it is called Mealy circuit. More about these are discussed in Chapter 11. Often, a state transition diagram of a sequential circuit serves better than the word description and is presented as final output of an analysis exercise.

Analysis of a sequential circuit can also be done through timing diagram where all the input, output and if necessary intermediate variables are plotted against some reference signal say, clock input. The timing diagram obtained by analyzing circuit of Fig. 8.37 is shown in Fig. 8.39. The method followed is given next.

Fig. 8.39 Timing diagram of the circuit given in Fig. 8.36

We start with an initial state B=0, A=0 and note that this state can only change when negative edge of the clock comes. The next state values of B and A are dependent on current inputs  $S_B$ ,  $R_B$  and  $S_A$ ,  $R_A$  at the time of clock trigger. As done before, these input values are derived following relations given in the circuit diagram, i.e.  $S_A=A'$ ,  $R_A=A$  and  $S_B=AB'$ ,  $R_B=A_B$  (suffix n can be ignored). For B=0, A=0 we get  $S_A=1$ ,  $R_A=0$ ,  $S_B=0$  and  $R_B=1$  and these values can change only when B and A change, i.e. in next clock cycle. Thus above values of SR inputs of two flip-flops continue till next negative edge of the clock. For  $S_B=0$  and  $R_B=1$ , at the negative edge of clock B remains at 0 (from truth table of SR flip-flop). Similarly for  $S_A=1$ ,  $S_A=0$  flip-flop A moves to 1. Thus we get B and A value of next clock cycle. Following above relation we now calculate SR input values of these flip-flops as  $S_A=0$ ,  $S_A=1$ ,  $S_B=1$  and  $S_B=0$  and these again remain constant up to next negative edge of the clock. Here as  $S_B=1$  and  $S_B=0$ ,  $S_B=0$  moves to 1 and as  $S_A=0$ ,  $S_B=0$ ,

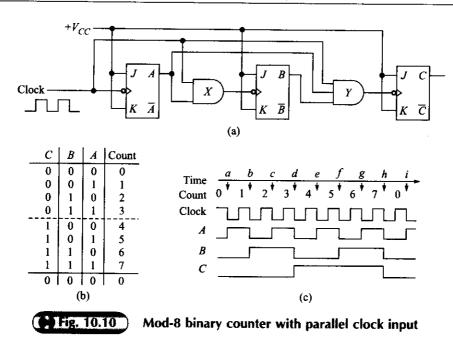

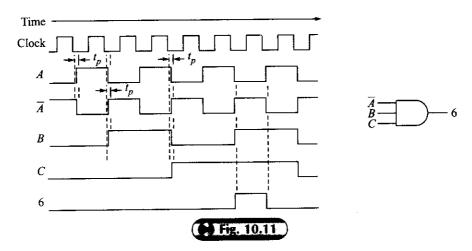

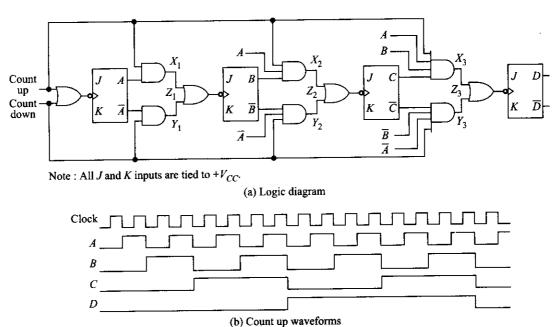

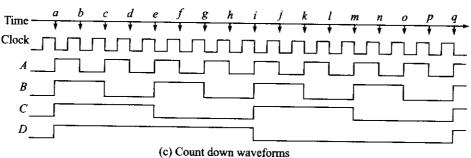

A detailed analysis of various configurations of counter and its timing diagram will be presented in Chapter 10.

- 21. What is analysis of sequential circuit?

- 22. Which of truth table and excitation table is useful for analysis of a sequential circuit?

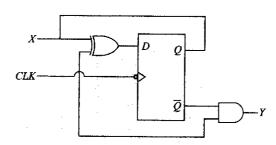

**Example 8.12** Explain the function of the circuit shown in Fig. 8.40 through state transition diagram.

Solution The D flip-flop input can be written as  $D = X \oplus Q_n$  and output  $Y = XQ'_n$ . Figure 8.41(a) shows the state table and Fig. 8.41(b) its state transition diagram. Note that, the circuit follows Mealy model and at any given state output is

generated from input to that state. Thus, outputs are shown by the side of the input in state transition diagram to right of the input and is separated by a '/' sign.

On careful observation, we can see something interesting in above circuit. If we ignore Y, then the D flip-flop block with Ex-OR gate as connected behaves like a T flip-flop where T = X.

Fig. 8.40

State transition diagram of Example 8.11

| $Q_n$ | X   | $D = X \oplus Q_n$ | $Q_{n+1}$ | $Y = X\overline{Q}_n$ |  |  |  |

|-------|-----|--------------------|-----------|-----------------------|--|--|--|

| 0     | 0   | 0                  | 0         | 0                     |  |  |  |

| 0     | 1   | 1                  | 1         | 1                     |  |  |  |

| 1     | 0   | 1                  | 1         | 0                     |  |  |  |

| _1    | 1   | 0                  | 0         | 0                     |  |  |  |

| -     | (a) |                    |           |                       |  |  |  |

Fig. 8.41

Solution to Example 8.11: (a) State table, (b) State transition diagram

### 8.12 CONVERSION OF FLIP-FLOPS: A SYNTHESIS EXAMPLE

Knowledge about how flip-flop of one type can be converted to another may be useful on various count. Say, when we have designed the circuit with one type and for implementation we get a different type from the store or the market. Redesign of the problem with available type of flip-flops may take considerable amount of time if the circuit is very complex. Instead one can convert the available type using few basic gate to the type in which design is done and implement the existing design.

Conversion of JK to SR, D, T is fairly straightforward as we see from their respective truth tables or characteristic equations. For example, one need not do anything extra to replace SR flip-flop from a design if SR flip-flop is not available, by JK flip-flop. This is because their truth tables are same except for input combination 11, which in design with SR flip-flop is taken care of not to appear in the input side. Hence, replacing SR with JK flip-flop does not pose any problem. However, the reverse is not true. In design with JK flip-flop there remains possibility of 11 appearing at input side and that combination of input is forbidden for SR flip-flop. Again, comparing truth tables or characteristic equations of JK and D flip-flops we see that putting an inverter from J to K (K = J) we get D flip-flop from JK flip-flop where J = D. T flip-flop can be obtained from JK flip-flop by making T = J = K.

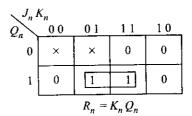

We show here how to convert an SR flip-flop to a JK flip-flop through a systematic approach, as a general methodology for synthesis or design of sequential logic circuit. A detailed study on various design problems and related issues are presented in Chapter 11.

In step one of this method, we look into JK flip-flop truth table and specifically note,  $Q_n \rightarrow Q_{n+1}$  transitions for a given combination of inputs JK and present state  $Q_n$ . Since the synthesis element is SR flip-flop we shall

refer to its excitation table to identify SR input combination for a required  $Q_n \rightarrow Q_{n+1}$  transition. Table 8.2 shows truth table of JK flip-flop as well as necessary SR inputs for  $Q_n \rightarrow Q_{n+1}$  transitions. Such tables are also known as *state synthesis table*.

Table 8.2 State Synthesis Table for SR to JK Flip-Flop Conversion

| $J_n$ | Kn | $Q_n$ | $\rightarrow Q_{n+1}$ | S <sub>n</sub> | $R_n$ |

|-------|----|-------|-----------------------|----------------|-------|

| 0     | 0  | 0     | 0                     | 0              | ×     |

| Ö     | 0  | 1     | 1                     | ×              | 0     |

| 0     | 1  | 0     | 0                     | 0              | ×     |

| 0     | 1  | 1     | 0                     | 0              | 1     |

| 1     | 0  | 0     | 1                     | 1              | 0     |

| 1     | 0  | 1     | 1                     | ×              | 0     |

| 1     | 1  | 0     | 1                     | 1              | 0     |

| 1     | 1  | 1     | 0                     | 0              | 1     |

The next step is to write SR inputs as a function of JK inputs and present state  $Q_n$ . Karnaugh Map derived from Table 8.2 for SR inputs are shown in Fig. 8.42 along with their design equations.

Fig. 8.42

Karnaugh Map and Design equations for SR inputs

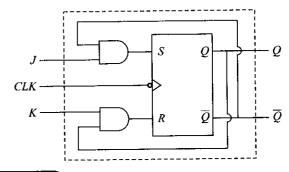

The final synthesized circuit developed from these equations, are shown in Fig. 8.43. The functional block within dotted lines made up of an *SR* flipflop and two AND gates, behave like a *JK* flip-flop.

Thus conversion between flip-flops, in simple cases can be done comparing their respective truth tables. For other cases, the steps shown above can be followed. Refer to Example 8.13 and Problems 8.30 to 8.32.

Fig. 8.43

Conversion of SR flip-flop to JK flip-flop.

- 23. Why flip-flop conversion is needed?

- 24. What is the basic difference between analysis and synthesis steps?

- 25. What is the difference between state analysis table and state synthesis table?

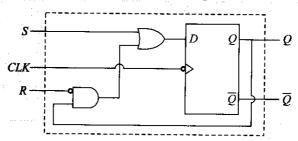

**Example 8.13**) Show how a D flip-flop can be converted to SR flip-flop.

Solution Note characteristic equation of two flip-flops.

For SR flip-flop:

$$Q_{n+1} = S + R'Q_n$$

and for D flip-flop:  $Q_{n+1} = D$

Thus with  $D = S + R'Q_n$  we get circuit shown in Fig. 8.44 which behaves like an SR flip-flop but made from a D flip-flop and basic logic gates. Method as shown in Section 8.11 also gives same solution.

### Fig. 8.44

Solution for Example 8.11. D flip-flop converted to SR flip-flop

### 8.13 HDL IMPLEMENTATION OF FLIP-FLOP

We continue our discussions on HDL from earlier chapters and in this section we look at how to represent a flip-flop using Verilog HDL. As discussed before, behavioral model is preferred for sequential circuit and always keyword is used in all these circuits. Since, sequential logic design also includes combinatorial design at some places we may use dataflow model for that. To start with let us see how a D latch (Fig. 8.15) and SR latch (Fig. 8.11) are expressed in HDL. We have used characteristic equation corresponding flip-flops given in Section 8.9. The explanation of the codes are simple. If EN = 1, output changes according to equation and if EN = 0, output does not change, i.e. remains latched to previous value.

```

module DLatch (D, EN, Q);

module SRLatch (S, R, EN, Q);

input D, EN;

input S, R, EN;

output Q;

output Q;

reg Q;

always @ (EN or D)

always @ (EN or S or R)

if (EN) Q=D:

if (EN) Q=S|(~R&Q);

//from characteristic equation

//from characteristic equation

endmodule

endmodule

```

Next we discuss how to describe a clocked flip-flop. The following Verilog code describes a D flip-flop with positive edge trigger, negative edge trigger and positive edge trigger with reset (CLR) given in Figs. 8.23 (a), (b) and (c) respectively. Here, the CLR input is active low, i.e. it clears the output (Q = 0) when CLR is 0. We use keywords posedge and negedge for this. With keyword always it ensures execution of always block once every clock cycle at corresponding edge. For asynchronous CLR we use a particular nomenclature of Verilog HDL. The always sensitivity list (after @) contains any number of edge statements including clock

and asynchronous inputs. The **always** block puts all asynchronous conditions in the beginning through else or **else if** and the *last* **else** statement responds to clock transition.

```

module DFFpos(D,C,Q);

module DFFneg(D,C,Q);

module DFFpos_clr(D,C,CLR,Q);

input D,C; //C is clock input D,C; //C is clock input D,C,CLR; //C is clock

output Q;

output Q;

output Q;

reg Q;

reg Q;

reg Q;

always@(posedge C)

always@(negedge C)

always@(posedgeCornegedgeCLR)

Q=D;

Q=D;

if (~CLR) Q=1'b0;

endmodule

endmodule

//Q stores 1 binary bit 0

else Q=D;

endmodule

```

### Example 8.14

Write a Verilog code that converts an D flip-flop to an SR flip-flop following Fig. 8.43 of Section 8.11

Solution The code is given as follows. See how combinatorial logic part of the circuit is expressed by assign statement.

```

module SRFFneg(S,R,C,Q);

input S,R,C; //C is clock

output Q;

wire DSR;

assign DSR = S!(~R&Q); //combinatorial logic shown in fig.8.45

DFFneg D1(DSR,C,Q); //instantiates negative edge triggered D FF

endmodule

module DFFneg(D,C,Q);

input D,C; //C is clock

output Q;

reg Q;

always @ (negedge C)

Q=D;

endmodule

```

# Example 8.15

Explain the use of following Verilog code in test bench preparation of sequential logic

```

Initial

begin

clk = 1'b0;

repeat (20)

#50 clk = ~clk;

end

```

Solution The keyword initial says following code is run for once. The variable 'clk' is of 1 binary digit and is initialized with 0 at time = 0. Keyword repeat ensures repetition of following statement 20 times. In that statement,

variable clk is complemented after a delay of 50 ns. Thus, clk toggles between 1 and 0 every 50 ns and for 20 times generating 10 cycles of 50 + 50 = 100 ns duration each. In a test bench, clk can be fed as clock input to simulate a sequential circuit for a finite duration. The number of clock pulse generated can be changed by changing number after repeat and clock period can be changed by changing delay after # sign.

### Example 8.16

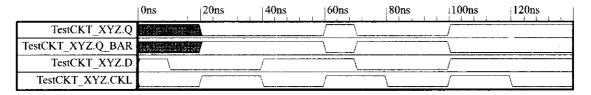

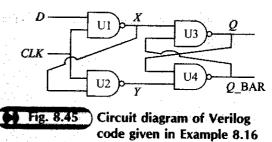

The Verilog code given in first column generates output given in second column and corresponding timing waveform is given next. Draw the digital circuit diagram from Verilog code and explain the output.

```

module CKT XYZ(Q,Q BAR,D,CLK);

output Q,Q BAR;

input D, CLK;

wire X, Y;

nand U1 (X, D, CLK);

0

CLK = 0, D = 1, Q = x

CLK = 0, D = 0, Q = x

nand U2 (Y,X,CLK) ;

10

CLK = 1, D = 0, Q = 0

nand U3 (Q,Q BAR,X);

20

CLK = 0, D = 1, Q = 0

nand U4 (Q BAR,Q,Y);

endmodule

60

CLK = 1, D = 1, Q = 1

module TestCKT_XYZ;

wire Q, Q_BAR;

70

CLK = 1, D = 0, Q = 0

CLK = 0, D = 0, Q = 0

80

reg D, CLK;

100

CLK = 1, D = 1, Q = 1

CKT_XYZ xyz(Q, Q_BAR, D, CLK);

120

CLK = 0, D = 1, Q = 1

initial

begin

$monitor($time, "CLK = %b, D= %b,

Q= %b\n", CLK, D, Q);

D=1;CLK=0;

#10 D = 0;

#30 D = 1; #30 D = 0;

#30 D = 1;

#40 $finish; /* the module will terminate after

140ns*/

end

always

#20 CLK = \simCLK;

endmodule

```

Solution The circuit diagram from the structural model given in the code is shown in Fig. 8.45. The test bench displays in the monitor time elapsed and CLK, D, Q (in binary) through first statement after begin. D initially 1 toggles after a delay of 10 ns, 30 ns, 30 ns, 30 ns, 30 ns. Simulation stops after further 40 ns taking a total time of 10 + 30 + 30 + 30 + 40 = 140 ns. Clock toggles at every 20 ns starting with a value 0.

The circuit shows that if CLK = 0, U1 and U2 outputs are 1 irrespective of other inputs and Q, Q BAR remains latched to previous value through cross coupled U3 and U4. When CLK = 1, D can change U1 output such that X = D' also final output Q = D. The timing diagram shows Q BAR = Q'. Thus the circuit behaves like a high level triggered D Flip-Flop.

### PROBLEM SOLVING WITH MULTIPLE METHODS

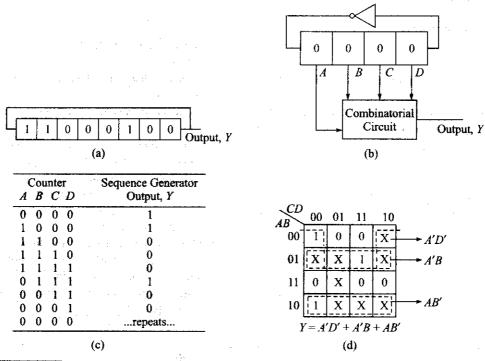

### Problem

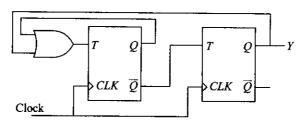

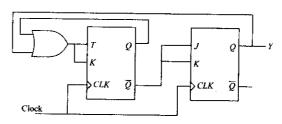

Analyze the circuit shown in Fig. 8.46 and find the output Y. Consider that the flip-flops are initially reset.

Fig. 8.46 A 7 flip-flop based circuit for analysis purpose

Solution We follow three different methods to analyze the circuit and identify the performance of Y.

In Method-1, we use state table approach. We make use of the fact that a T flip-flop does not change its state if T=0 but it toggles when T=1 at the clock trigger.

Let us name the first flip-flop as X and its input and output as  $T_X$  and X respectively. Similarly, let the second flip-flop be named Y and its input is  $T_Y$  while its output is already assigned as Y. Then, the state table is shown in Fig. 8.47. We find that the circuits move from states  $00, 01, 10, 00, \ldots$  repetitively and the output Y goes HIGH once in three cycles and remains HIGH for one clock period.

| S | Clock cycle $X_n Y_n$ | $T_{\mathbf{X}} = X_n + Y_n$ | $T_Y = X'_n$ | $X_{n+1}$ | $Y_{n+1}$ |

|---|-----------------------|------------------------------|--------------|-----------|-----------|

| _ | 0 0 0                 | 0                            | 1            | 0         | 1         |

|   | 1 0 1                 | 1                            | 1            | 1         | 0         |

|   | 2 1 0                 | 1                            | 0            | 0         | 0         |

### Fig. 8.47

State Table to analyze circuit diagram of Fig. 8.47

In Method-2, we make use of the characteristic equation of T flip-flop.

From Section 8.9, we know that  $Q_{n+1} = TQ'_n + T'Q_n$

By following similar X and Y naming of two flip-flops as in Method-1, we find that

input:

$$T_X = X_n + Y_n$$

output:  $X_{n+1} = (X_n + Y_n)X'_n + (X_n + Y_n)'X_n$

$= Y_nX'_n + X'_n Y'_n X_n$

$= Y_nX'_n$

input:  $T_Y = X'_n$

output:  $Y_{n+1} = X'_n Y'_n + (X'_n)'Y_n$

$= X_n' Y_n' + X_n Y_n$

For Yflip-flop,

The final solution is shown in Fig. 8.48.

| $X_n$ | $Y_n$ | $X_{n+1} = Y_n X_n'$ | $Y_{n+1} = X_n' Y_n' + X_n Y_n$ |

|-------|-------|----------------------|---------------------------------|

| 0     | 0     | 0                    | 1                               |

| 0     | 1     | 1                    | 0                               |

| 1     | 0     | 0                    | 0                               |

| 0     | 0     | repe                 | ats                             |

## Fig. 8.48

**Solution using Method-2**

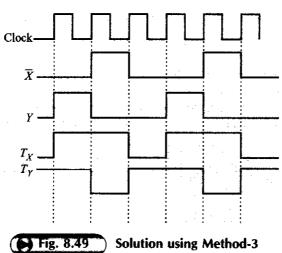

In Method-3, we make use of the timing diagram as shown in Fig. 8.49. We note that the flip-flops are positive edge triggered. The *T* input just before the positive edge decides output of the flip-flop in next cycle.

We start with initial XY = 00. Then we draw  $T_X$  by ORing X and Y waveforms and  $T_Y$  by inverting Y waveform.  $T_X$  and  $T_Y$  before positive edge decide value of X and Y respectively in next clock cycle (from T flip-flop truth table).

# **SUMMARY**

A flip-flop is an electronic circuit that has two stable states. It is said to be bistable. A basic RS flip-flop, or latch can be constructed by connecting two NAND gates or two NOR gates in series with a feedback connection. A signal at the set input of an RS flip-flop will force the Q output to become a 1, while a signal at the reset input will force Q to become a 0.

A simple RS flip-flop or latch is said to be transparent—that is, its output changes state whenever a signal appears at the R or S inputs. An RS flip-flop can be modified to form a clocked RS flip-flop whose output can change states only in synchronism with the applied clock.

An RS flip-flop can also be modified to form a D flip-flop. In a D latch, the stored data may be changed while the clock is high. The last value of D before the clock returns low is the data that is stored. With edge-triggered D flip-flops, the data is sampled and stored on either the positive or negative clock edge.

The values of *J* and *K* determine what a *JK* flip-flop does on the next clock edge. When both are low, the flip-flop retains its last state. When *J* is low and *K* is high, the flip-flop resets. When *J* is high and *K* is low, the flip-flop sets. When both are high, the flip-flop toggles. In this last mode, the *JK* flip-flop can be used as a frequency divider.

There are various ways to represent a flip-flop like truth table, characteristic equation, state transition diagram or excitation table. Flip-flop treated as a finite state machine highlights its functional aspect. Analysis of a sequential circuit helps to understand performance of a given circuit in a systematic manner and through synthesis we develop circuit diagram for a specified problem.

# **GLOSSARY**

- asynchronous Independent of clocking. The output can change without having to wait for a clock pulse.

- bistable Having two stable states.

- bistable multivibrator Another term for an RS flip-flop.

- buffer register A group of memory elements, often flip-flops, that can store a binary word.

- characteristic equation logic expression describing a flip-flop.

- edge triggering A circuit responds only when the clock is in transition between its two voltage states.

- finite state machine functional description of sequential circuit.

- flip-flop An electronic circuit that has two stable states.

- hold time The minimum amount of time that data must be present after the clock trigger arrives.

- latch Another term for an RS flip-flop.

- Mealy model output is dependent both on current state and input to the circuit.

- Moore model output is dependent only on current state of the circuit.

- propagation delay The amount of time it takes for the output to change states after an input trigger.

- setup time The minimum amount of time required for data inputs to be present before the clock arrives.

- state the set of memory values at any given time for a sequential logic circuit.

- synchronous When outputs change states in time with a clock. A clock signal must be present in order for the outputs to change states.

- transparent The condition that exists when the flip-flop output changes immediately after its inputs (R, S, J, K, D) change state.

### **PROBLEMS**

### Section 8.1

- 8.1 List as many bistable devices as you can think of—either electrical or mechanical. (*Hint:* Magnets, lamps, relays, etc.)

- 8.2 Redraw the NOR-gate flip-flop in Fig. 8.3b and label the logic level on each pin for R = S = 0. Repeat for R = S = 1, for R = 0 and S = 1, and for R = 1 and S = 0.

- 8.3 Redraw the NAND-gate flip-flop in Fig. 8.7a and label the logic level on each pin for  $\overline{R} = \overline{S} = 0$ . Repeat for  $\overline{R} = \overline{S} = 1$ , for  $\overline{R} = 1$ , and  $\overline{S} = 0$ , and for  $\overline{R} = 0$  and  $\overline{S} = 1$ .

- 8.4 Redraw the NAND-gate flip-flop in Fig. 8.8a and label the logic level on each pin for R = S = 0. Repeat for R = S = 1, for R = 0 and S = 1, and for R = 1 and S = 0.

## Section 8.2

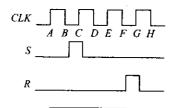

- 8.5 The waveforms in Fig. 8.50 drive the clocked RS flip-flop in Fig. 8.11. The clock signal goes from low to high at points A, C, E, and G. If Q is low before point A in time:

- a. At what point does Q become a 1?

- b. When does Q reset to 0?

### Fig. 8.50

- 8.6 Use the information in the preceding problem and draw the waveform at Q.